# LrGAN: A Compact and Energy Efficient PIM-based Architecture for GAN Training

Haiyu Mao, Member, IEEE, Jiwu Shu, Fellow, IEEE, Mingcong Song, Member, IEEE, Tao Li, Fellow, IEEE

**Abstract**—As a powerful unsupervised learning method, Generative Adversarial Network (GAN) plays an essential role in many domains. However, training a GAN imposes four more challenges: (1) intensive communication caused by complex train phases of GAN, (2) much more ineffectual computations caused by peculiar convolutions, (3) more frequent off-chip memory accesses for exchanging intermediate data between the generator and the discriminator and (4) high energy consumption of unnecessary fine-grained MLC programming. In this paper, we propose LrGAN, a PIM-based GAN accelerator, to address the challenges of training GAN. We first propose a zero-free data reshaping scheme for ReRAM-based PIM, which removes the zero-related computations. We then propose a 3D-connected PIM, which can reconfigure connections inside PIM dynamically according to dataflows of propagation and updating. After that, we propose an approximate weight update algorithm to avoid unnecessary fine-grain MLC programming. Finally, we propose LrGAN based on these three techniques, providing different levels of accelerating GAN for programmers. Experiments show that LrGAN achieves 47.2×, 21.42×, and 7.46× speedup over FPGA-based GAN accelerator, GPU platform, and ReRAM-based neural network accelerator respectively. Besides, LrGAN achieves 13.65×, 10.75×, and 1.34× energy saving on average over GPU platform, PRIME, and FPGA-based GAN accelerator, respectively.

Index Terms—Processing In Memory, Generative Adversarial Network, Approximate Computing, Non-Volatile Memory.

# **1** INTRODUCTION

TREMENDOUS success has been fueled by supervised deep learning in image classification, speech recognition, and so on [32] [60] [34] [62] [52] [23] [26]. However, non-trivial amount of training datasets with millions of lables prevents high-accuracy supervised deep learning from being employed in many domains where massive labels are either unavailable or costly to collect through human effort.

By automatically generating richer synthetic datasets without labeling data sets, semi-supervised learning [9] [28] and unsupervised learning [25] [21] [18] are promising to extend the intelligence of deep learning. On the frontier, GAN is the most popular unsupervised learning method, effectively working in many domains, such as video prediction [21], autonomous driving [22] and photo resolution upgrading [35].

Though GAN is powerful to generate items without labeling training sets by human, its network structure is more complex than traditional NN's to efficiently execute on hardware. The generator model and discriminator model of GAN collaboratively work in a minimax manner, to achieve stronger GAN with higher accuracy. To uphold the interaction between the two models, massive amount of intermediate data is required to be communicated between the two models frequently. Since there are quite limited onchip memory space to store intermediate data, GAN train-

Manuscript received Sep 27, 2019; revised Apr 12, 2020. (Corresponding author: Jiwu Shu.)

ing will introduce additional pressure on off-chip memory accesses, which consume nearly two orders of magnitude more energy than a floating point operation [20]. Thus, these huge data movements become a bottleneck of the system design for GAN.

To solve the memory wall problem in GAN training, researchers proposed ReRAM-based Processing In Memory (PIM) [40] [15] [58] [7] [61], which exhibits energy efficiency in reducing memory access cost compared with CPUs and GPUs. Besides, it can complete a Matrix-Multiply-Vector (MMV) operation in almost only one read cycle with low energy consumption. Since MMV operations dominate the computation patterns in GAN training, ReRAM-based PIM technologies have the potential to reduce memory access cost and accelerate GAN training efficiently.

However, GAN has two main features which are different from traditional neural networks: (1) zero-insertion during training phase; (2) intricate dataflow patterns between the two models. These two features degrade the efficiency of the PIM-based accelerator for GAN. First, zero-insertion adds a heavy burden on storage. Also, I/O traffic becomes the system bottleneck because (1) the interaction between generator and discriminator requires more communication via I/Os in PIM. (2) complex dataflow of GAN exists irregular data dependencies. Therefore, limited I/O bandwidth stalls GAN training. Moreover, ReRAM-based PIM employs MLC (Multi-Level Cell), which consumes a large amount of energy during programming, hindering the low-power ReRAM-based GAN training.

To address these challenges in PIM-based GAN architecture, we first propose a novel, software-managed Zero Free Data Reshaping (ZFDR) scheme to remove all the zero-related operations produced by GAN. Then, we propose a reconfigurable 3D connection architecture, which not

Haiyu Mao and Jiwu Shu are with the Department of Computer Science and Technology, Tsinghua University, Beijing, 100084, China. E-mail: mhy15@mails.tsinghua.edu.cn, shujw@tsinghua.edu.cn

<sup>•</sup> Mingcong Song and Tao Li are with the Department of Electrical and Computer Engineering, University of Florida, FL, 32603, US. E-mail: songmingcong@ufl.edu, taoli@ece.ufl.edu

only efficiently fits complex dataflows of GAN, but also supports efficient ReRAM reads and writes and hides the I/O overhead to a great extent. What's more, we propose an approximate weight update algorithm to eliminate the high energy-consuming portion of programming an MLC. Finally, we propose LrGAN<sup>1</sup> (based on LerGAN [48]), a ReRAM-based 3D connection GAN accelerator with low energy consumption, which carefully maps the data processed by ZFDR to the 3D-connected PIM. By doing so, it not only achieves higher I/O performance but also enables I/O connection configuration flexibly for the complex dataflows in GAN training. Experiments show that LrGAN achieves  $47.2\times$ ,  $21.42\times$ , and  $7.46\times$  speedup over FPGA-based GAN accelerator, GPU platform, and ReRAM-based neural network accelerator respectively. Moreover, LrGAN achieves  $13.65\times$ ,  $10.75\times$ , and  $1.34\times$  energy saving on average over GPU platform, PRIME, and FPGA-based GAN accelerator, respectively.

The main contributions of this paper are as follows:

(1) We elaborate three steps of zero-inserting that enable transposed convolution operations in GAN and further analyze the amount of zeros in GAN training. To address problems caused by massive zeros in ReRAM-based PIM, we propose Zero-Free Data Reshaping (ZFDR) to remove zero-related operations. ZFDR is flexible to support different paddings, strides and kernel sizes, capable of handling both existing GANs and future GANs with larger stride (e.g. stride of 3).

(2) We present the dataflows of training GAN in detail and propose a novel reconfigurable 3D-connected PIM to handle the complicated dataflows. Our 3D connection supports efficient data transferring of both propagation and updating. It is worth mentioning that, to the best of our knowledge, we are the first to study efficient connections in ReRAM-based PIM.

(3) We propose an approximate weight update algorithm to avoid energy-inefficient operations in the fine-grain MLC programming. The hardware which supports the approximate update scheme has a negligible modification on the circuit of data-comparison-write.

(4) We propose LrGAN based on ZFDR, approximate weight update and 3D-connected PIM. We make slight modifications on the software (via providing interfaces for ZFDR) and memory controller (via creating a finite-state machine for data mapping and configuration of switches) to enable LrGAN to combine ZFDR and 3D-connected PIM well. Also, we enable programmers to use heterogeneous levels of acceleration according to demands.

The rest of this paper is organized as follows. We first introduce ReRAM-based PIM and GAN in Section 2. Then we analyze the challenges of using PIM to accelerate GAN training in Section 3. We present our ZFDR, approximate weight update algorithm and 3D-connected PIM in Section 4. The design of LrGAN is in Section 5. Section 6 evaluates the proposed algorithms, 3D-connected PIM and LrGAN system. Finally, we present related works and conclusions in Section 7 and Section 8 respectively.

# 2 BACKGROUND

This section first introduces ReRAM-based PIM and how it can be utilized to implement NNs efficiently, then presents GAN and its features.

# 2.1 ReRAM-based PIM

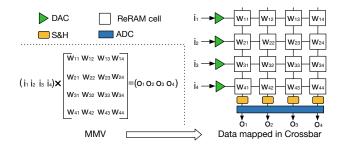

Fig. 1. Mapping MMV to ReRAM Crossbar.

ReRAM stands out from other non-volatile memories (NVMs) since it has high density, relatively low write latency [67], and low write energy [49]. Moreover, it has high endurance (>  $10^{10}$  [36] [37], up to  $10^{12}$  [37] [27], much higher than that of PCM, which is  $10^7 \sim 10^8$  [56]). If a network needs to be trained for  $10^5$  times [43], ReRAM-based PIM can train  $10^5 \sim 10^7$  such networks. Due to these benefits of ReRAM, recent studies [15] [58] [61] [14] modify it as the hardware of PIM to accelerate the inference and training of NNs.

ReRAM-based PIM consists of ReRAM arrays and peripheral circuits. Note that, ReRAM arrays can be configured to either support MMVs (called CArrays in this paper), or be used as traditional storage (called SArrays in this paper). When ReRAM arrays are configured as CArrays, they store weights of NNs and conduct MMVs by feeding corresponding inputs (briefly shown in Fig.1). ReRAMbased PIM also has buffer which is composed of ReRAM cells and connected to CArrays directly. Such buffer is called BArray and enables CArray to access it randomly, hiding the memory access time when performing computation [15]. Equipped with CArrays, BArrays and peripheral circuits to support various basic computations, ReRAM-based PIM can be used to accelerate NNs efficiently.

#### 2.2 Generative Adversarial Network

The Generative Adversarial Network (GAN) consists of two components: a discriminator and a generator. The discriminator learns to decide whether a sample is from the real data set or the generator. The generator aims to generate a sample close to the real data to confuse the discriminator. Therefore, in GAN, the two components play a minimax game to compete with each other iteratively. A minibatch stochastic gradient descent method can be used to train this model, where in each training iteration, a minibatch of *m* noise samples  $\{n_1, n_2, ..., n_m\}$  and *m* true examples  $\{x_1, x_2, ..., x_m\}$  are sampled from a prior noise distribution  $p_e(n)$  and real data distribution  $p_d(x)$ , respectively. We use  $G(n; \theta_g)$  to denote the generative model that generates samples from noises with parameters  $\theta_g$  and D(x) to denote the discriminative model that represents the probability that

<sup>&</sup>lt;sup>1</sup> "Lr" comes from removing "o" from "zero" which represents removing 0, changing "z" to "l" to represent shortening wire connection, and deleting "e" to represent energy-saving.

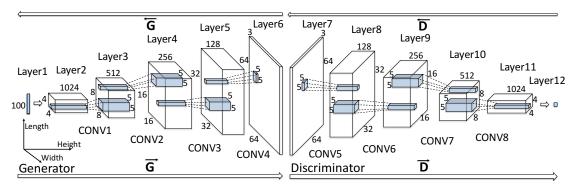

Fig. 2. DCGAN Outline

x comes from the real data distribution  $p_d(x)$ . In order to optimize the discriminator, it needs to be updated by ascending its stochastic gradient using Equation 1, which means that the discriminator can assign correct labels to both training examples from D and samples from G. In order to maximize the generator, GAN uses Equation 2 to update it by descending its gradient, which tries to confuse the discriminator to predict the samples as data from the real data distribution. In conclusion, GAN will converge eventually so that the generator can generate an example which is similar to a real one.

$$\nabla_{\theta_d} \frac{1}{m} \sum_{i=1}^{m} [\log D(x_i) + \log(1 - D(G(n_i)))]$$

(1)

$$\nabla_{\theta_g} \frac{1}{m} \sum_{i=1}^{m} \log(1 - D(G(n_i)))$$

(2)

We take the most popular Deep Convolutional Generative Adversarial Network (DCGAN) [71] as an example to further introduce GAN. The framework of DCGAN is shown in Fig.2. There are some differences between traditional Convolutional Neural Network (CNN) and DC-GAN in training phase. In forward propagation phase of discriminator, DCGAN employs strided convolution (S-CONV) instead of pooling. As shown in Fig.2, the generator has an inverse structure of discriminator, and it employs transposed convolution (T-CONV) in forward propagation phase.

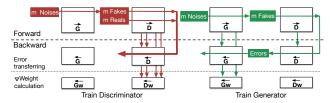

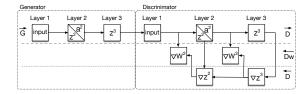

Fig. 3. Dataflows of Training Discriminator and Generator of DCGAN

Fig.3 shows dataflows of training DCGAN and Table 1 shows notations for explanation of training DCGAN. Overall, training DCGAN involves two major parts: one is forward propagation and the other is backward propagation. The backward propagation has two main sub-tasks: error transferring and  $\nabla$ weight calculation. When training the discriminator, the generator produces *m* fake samples using *m* noises (*m* is the batch size and a noise (input) is denoted

TABLE 1 Notations Used for Explanation of Training DCGAN.

| Symbol       | Description                                         |

|--------------|-----------------------------------------------------|

| $W^l$        | Kernel weights for <i>l</i> -th layer               |

| $\nabla W^l$ | Derivative of kernel weights for <i>l</i> -th layer |

| $z^l$        | Value of $(W^l)^T x + b$                            |

| $\nabla z^l$ | Derivative of $z$ for $l$ -th layer                 |

| g            | Active function                                     |

| $a^l$        | Value of $g(z^l)$                                   |

as a vector with 100 elements shown in Layer1 of Fig.2). This step is denoted by  $\overrightarrow{G}$ , where DCGAN conducts T-CONV. Then, one batch of real samples and one batch of fake samples are fed into the discriminator. This step is denoted by  $\overrightarrow{D}$ , where DCGAN conducts S-CONV. Next, DCGAN computes the error of output layer  $\nabla z^L$  using the loss function Equation 1, where L is the last layer of the discriminator. After that, DCGAN feeds  $\nabla z^L$  back to the network and begins the backward propagation, which consists of two stages  $\overleftarrow{D}$  and  $\overleftarrow{D_w}$ . Firstly,  $\nabla z^L$  is fed back layer by layer in  $\overleftarrow{D}$  using Equation 3 (\* denotes an elementwise multiplication). Therefore, in  $\overleftarrow{D}$ , the T-CONV takes  $\nabla z^{l+1}$  and  $z^l$  cached by  $\overrightarrow{D}$  as inputs then outputs  $\nabla z^l$ .

$$\nabla z^{l} = (W^{l+1})^{T} \nabla z^{l+1} * g'(z^{l})$$

(3)

Conducting  $\overleftarrow{D_w}$  needs  $\nabla z^l$  transferred by  $\overleftarrow{D}$  and the intermediate  $a^{l-1}$  cached by  $\overrightarrow{D}$ . Equation 4 shows the computation in  $\overleftarrow{D_w}$ , denoted as W-CONV of discriminator since it is different from both S-CONV and T-CONV.

$$\nabla W^l = a^{l-1} \nabla z^l \tag{4}$$

After  $\overleftarrow{D_w}$ , the discriminator is updated with  $\nabla W^l$ . When training the generator, the generator generates m samples and feeds them into the discriminator. After conducting  $\overrightarrow{D}$ , according to the Equation 2, the error of the output layer in discriminator is sent to  $\overleftarrow{D}$ . With the intermediate  $z^l$ cached by  $\overrightarrow{D}$ ,  $\overleftarrow{D}$  can calculate errors and send them to error propagation of generator (denoted as  $\overleftarrow{G}$ ). With  $\nabla z^l$  sent by  $\overleftarrow{G}$  and the intermediate  $a^{l-1}$  cached by  $\overrightarrow{G}$ ,  $\overleftarrow{G_w}$  can calculate  $\nabla W^l$  of generator. After that, the generator is updated with  $\nabla W^l$ .

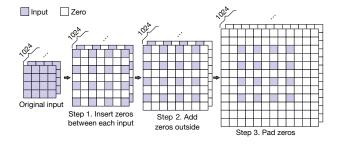

Fig. 4. Steps of Adding Zeros in Inputs of CONV1.

Fig. 5. Convolution on Inserted Zeros Inputs with Stride of 1.

# 3 CHALLENGES

Although GAN has two networks, each of which resembles CNN, it manifests some differences from traditional CNN. In this section, we discuss challenges for PIM-based NN accelerator to execute GAN.

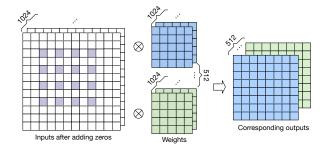

## 3.1 Redundant Zero-Related Operations

Since DCGAN employs S-CONV, its training introduces considerable zero-insertion, increasing burden on both storage and bandwidth. In order to explain how redundant zeros are introduced and restrain the efficiency, we first introduce some notations used in this paper in Table 2 and take CONV1 of the generator in Fig. 2 as an example of T-CONV. As shown in Fig. 2,  $I_w = I_l = 4$  and  $O_w = O_l = 8$ . The converse convolution of CONV1 is the same as CONV8 in Discriminator, so  $S^{'} = 2$ , S = 1,  $P^{'}_{w} = P^{'}_{l} = 2$ ,  $P_w = P_l = 2$ . Also, CONV1 and CONV8 have the same size of kernel weight. To conduct CONV1, we first insert one zero between every two adjacent input numbers horizontally and vertically (Step 1), then add one zero at the end of input (Step 2) and finally use zero padding of 2 (Step 3). After that, we convolute it with 512 kernels, whose  $W_w$ =  $W_l$  = 5 and  $W_h$  is 1024. Eventually, we obtain an output whose size is  $8 \times 8 \times 512$ . In this example, we store and transfer 147456 input values while only 16384 of them are useful. Moreover, we conduct 1638400 multiplications while 295936 of them are useful, whose efficiency is only 18.06%.

In general,  $I_w = I_l$ ,  $O_w = O_l$ ,  $P_w = P_l$  and  $P'_w = P'_l$ . So we denote them as I, O, P and P', respectively, and their relationship is described in Equation 5.

$$\frac{O+2P^{'}-W}{S^{'}}=(I-1)\cdots R \quad (R \text{ is the remainder}) \quad (5)$$

TABLE 2 Notations Used for Explanation of Convolution Operations.

| Symbol            | Description                                      |  |  |  |

|-------------------|--------------------------------------------------|--|--|--|

| $I_w, I_l, I_h$   | Width, length, height of input                   |  |  |  |

| $O_w, O_l, O_h$   | Width, length, height of output                  |  |  |  |

| $W_w, W_l, W_h$   | Width, length, height of kernel weight           |  |  |  |

| $N_w$             | Number of kernel weights                         |  |  |  |

| S                 | Stride size of convolution                       |  |  |  |

| S'                | Stride size of converse convolution              |  |  |  |

| $P_w, P_l$        | Padding on width, length                         |  |  |  |

| $P'_w, P'_l$      | Padding on width, length of converse convolution |  |  |  |

| N <sub>iz_w</sub> | Number of insert zeros on width                  |  |  |  |

| N <sub>iz_l</sub> | Number of insert zeros on length                 |  |  |  |

| Nzero             | Number of zeros                                  |  |  |  |

Generally, to conduct a convolution in the generator, we first insert S' - 1 zeros between every two input numbers, then we add R zeros at the end and finally we use zero padding of P (where P = W - P' - 1). Based on the operations above, we can calculate  $N_{iz_w}$  and  $N_{zero}$ .

$$N_{iz\_w} = N_{iz\_l} = (S' - 1) \times (I - 1) + R$$

(6)

$$N_{zero} = (N_{iz\_w} + I_w + P_w) \times (N_{iz\_l} + I_l + P_l) - I_w \times I_l$$

(7)

From Equation 6 and Equation 7 we can observe that with the increase of S' and P, the issue of redundant zeros in T-CONV becomes more severe.

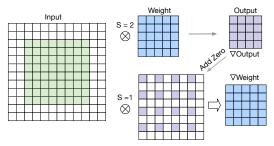

Similar to T-CONV, W-CONV of a generator needs to insert zeros into inputs. However, W-CONV of a discriminator needs to insert zeros to both inputs and kernels. We take a W-CONV connecting Layer11 and Layer10 in Fig.2 as an example. For simplicity, we take one input feature map to illustrate the difference of zero-insertion between W-CONV and T-CONV in the example.

As shown in Fig.6, in the forward propagation, given a  $8 \times 8$  input, we first pad it with 2, then convolve it with a  $5 \times 5$  kernel, and finally obtain a  $4 \times 4$  output. In the backward propagation, we denote  $\nabla$ Output as dz in Equation 3, whose shape is the same as the output. We first insert zeros to  $\nabla$ Output and regard  $\nabla$ Output as a kernel weight. Then, we convolute the given  $8 \times 8$  input with the kernel weight to obtain  $\nabla$ Weight.

For W-CONV of the discriminator, the relationship between input and output can be described as Equation 8.

$$\frac{I+2P-W}{S} = (O-1)\cdots R \quad (R \text{ is remainder}) \quad (8)$$

Furthermore, the relationship between  $N_{iz_w}$  and  $N_{iz_l}$  of the kernel weight can be described as Equation 9.

$$N_{iz_w} = N_{iz_l} = (S-1) \times (O-1) + R$$

(9)

According to Fig.6,  $N_{zero}$  in W-CONV of the discriminator equals to the sum of the number of zeros used for input padding and the number of zeros used for  $\nabla$  insertion. It can be described using Equation 10.

$$N_{zero} = [(N_{iz\_w} + O_w) \times (N_{iz\_l} + O_l) - O_w \times O_l] + [(I_w + P_w) \times (I_l + P_l) - I_w \times I_l]$$

(10)

Fig. 6. An Example of W-CONV of Discriminator.

Fig. 7. Dataflow of Training Discriminator.

Fig. 8. Dataflow of Training Generator.

Fig. 9. Networks Mapped to H-tree Connected Tiles.

For W-CONV of the discriminator,  $N_{zero}$  also increases either *S* or *P* increases according to Equations 9 and 10.

## 3.2 Inefficient I/O Connection

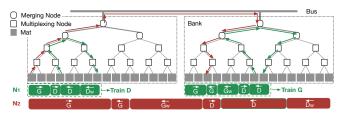

For training where massive memory reads/writes are required to update kernel weights, PipeLayer [61] employs efficient H-tree wire routing. However, the dataflows of GAN training are more complicated than that of traditional NNs. We take a simple GAN (3-layer generator and 3-layer discriminator) as an example to show details of dataflows (training discriminator in Fig.7 and training generator in Fig.8). Thus, if we train a GAN by mapping phases to H-tree connection architecture, it will experience a large number of long routings.

Fig.9 shows two GAN examples  $N_1$ ,  $N_2$  training on the H-tree routing banks. Each bank has 16 tiles and each tile is composed of several CArrays, BArrays and SArrays. There are two kinds of routing nodes: (1) multiplexing node, connecting data wires of the same width; (2) merging node, through which the width of data wire is divided into two halves. In the examples shown in Fig.9,  $N_1$  is a relatively small GAN, while  $N_2$  may be a bigger GAN or a small GAN with high parallelism (i.e. duplicating kernel weights for

Fig. 10. Programming Scheme of MLC.

several times). In other words, the space utilized by training a GAN is decided by the size of GAN itself and the number of kernel weight duplications. When we map a GAN, we can separately training discriminator and generator as  $N_1$ shows. This introduces more space while reduces total data movements compared with the map without duplication like the mapping pattern of  $N_2$ . However, all of these mapping patterns suffer from long routings, as examples marked in green and red arrows shown in Fig.9. With network size and number of duplications increasing, this problem becomes more severe. We can relieve this problem by adding some connections between the routing nodes whose parent nodes are different, as the connection pattern used in by MAERI [33]. Since the dataflow of GAN training is much more complicated, simply doing so will not achieve desirable performance of speedup.

## 3.3 High Energy-consuming Write Scheme of MLC

ReRAM-based PIM [14], [15], [58], [61] employs MLC instead of SLC for the following three reasons. (1) Using SLCbased NVM array to conduct a vector-matrix multiplication requires more time for intermediate data processing. (2) The SLC-based array not only has latency overhead for processing intermediate data but also introduces larger peripheral circuit to process intermediate data. (3) MLC-based NVM has higher memory density than MLC-based NVM.

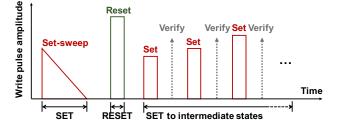

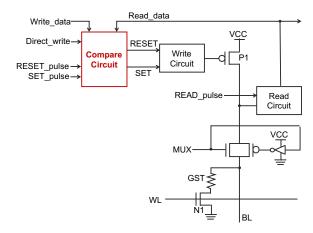

Although MLC has these three advantages over SLC, its programming is more complex than that of SLC, which only conducts a single SET or RESET operation. Figure 10 depicts the procedure for programming an MLC, which is also known as "Program-and-Verify" (P&V). First, a SET-sweep pulse is applied to program the cell to its lowest resistance state. This is followed by a RESET to initialize the cell to a total RESET state. Next, P&V applies an SET pulse and then verifies that a specified resistance has been achieved, iteratively. The protracted programming procedure mentioned above accounts for MLC's long write latency and high energy consumption. Based on this programming scheme, we can also figure out that altering values varies time and energy consumption.

TABLE 3 Programming Latency and Energy of MLC ReRAM Cell.

| Target        | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

|---------------|------|------|------|------|------|------|------|------|

| $T_{WC}(ns)$  | 15.2 | 46.8 | 98.3 | 143  | 150  | 101  | 52.7 | 12.1 |

| $E_{ave}(pJ)$ | 2.0  | 6.7  | 19.3 | 35.1 | 35.6 | 19.6 | 8.5  | 1.5  |

Table 3 is retrieved from [53]. It records the worst case of latency and the average energy consumption for programming 3-bit MLC (eight resistance states). An MLC costs more

time and energy to program a cell to middle resistance states (e.g., state 3, 4 in 3-bit MLC) since it requires additional tuning iterations. Moreover, time and energy consumption spike with 4-bit MLC due to the finer-grained tuning procedure. Unfortunately, training GAN requires cells with more resistance levels, which improves performance and memory density. Since NVM-based PIM lacks flexibility when compared with FPGA and GPU, it should ensure both high performance and low energy consumption. Thus, MLC's energy inefficient write scheme has become a challenge for GAN training with ReRAM-based PIM.

# 4 OUR PROPOSED SOLUTIONS

In this section, we propose our solutions to address the three challenges analyzed in Section 3.

#### 4.1 PIM-Based Zero-Free Scheme

In order to address the problem mentioned in Section 3.1, we propose a novel software managed, memory controller supported scheme called ZFDR (Zero-Free Data Reshaping) to remove zero operations. This scheme consists of two components: (1) *T*-*CONV ZFDR* for T-CONVs; (2) *W*-*CONV-S ZFDR* for W-CONV of stride convolution.

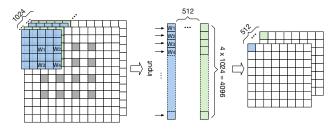

We first take CONV1 (Fig.5) as an example to explain our T-CONV ZFDR scheme. We usually convert convolutions into MMVs in PIM-based computation, so we first reshape kernel weights into vectors. The reshape operation is different from the general one since we only extract kernel weights that multiply non-zero inputs, as shown in Fig.11. After reshaping all the 512 weight kernels into a  $512 \times 4096$  matrix, we map this weight matrix into the Carray and feed the corresponding 4096 inputs, then we obtain 512 results. All of above operations correspond to one convolution operation with 512 kernel weights. After the first convolution operation shown in Fig.11, we slide kernel weights with stride of 1. When sliding, the useful kernel weights change. Fig.12 gives an example of how useful kernel weights change when sliding. Thus, in Step 3, the weight matrix can be reused since it is the same with that in Step 1. We find that some reshaped weight matrices are reused when kernels slide on the edge of input map and more reshaped weight matrices are reused when kernels slide inside the input map.

In summary, we store 25 kinds of reshaped weight matrix in this case (also the same in CONV2, CONV3 and CONV4). Notwithstanding this ZFDR scheme introduces more space to store weights, it improves parallelism greatly. For example, it only needs 9 cycles (one MMV uses one cycle) to complete CONV1. While without ZFDR, it will take 64 cycles. Moreover, if we duplicate kernel weights directly (without ZFDR), and we want to conduct CONV1 in 9 cycles, we need to store at least 179200 weights. It means that in order to achieve the same performance as ZFDR, duplicating weights directly not only consumes 75% more storage, but also transfers  $9 \times$  inputs.

In order to extend our ZFDR scheme to a general case, we first define the Loop Length (LL) using the following equation.

Fig. 11. Example of Zero Free Data Reshaping.

Fig. 12. Example of How Useful Weights Change When Sliding.

$$LL = \begin{cases} I \times S' + (S' - 1) & P \ge S' - 1\\ I \times S' & P < S' - 1, P + R \ge S' - 1\\ I \times S' - (S' - 1) & P < S' - 1, P + R < S' - 1 \end{cases}$$

(11)

Then we divide the T-CONV ZFDR scheme into three cases as follows. Case 1: Reshape kernel weights that conduct convolution on the corner of input map. This case has  $((I - 1) \times S' + 1 + R + 2P - LL)^2$  sets of reshaped weights, and each kind of weights is non-reusable. Case 2: Reshape kernel weights that conduct convolution on the edge of input map. We define  $R_1$ ,  $R_2$  using Equations 12 and 13:

$$R_{1} = \begin{cases} P & P < S' - 1 \\ P - (S' - 1) & else \end{cases}$$

(12)

$$R_{2} = \begin{cases} (P+R) - (S'-1) & P+R \ge S'-1 \\ P+R & else \end{cases}$$

(13)

Then number of reshaped kernel weights in this case is  $R_1 \times S' \times 2 + R_1 \times S' \times 2$ , and each reshaped kernel weight can be reused by t times ( $t \in \left\{ \left\lfloor \frac{LL-W+1}{S'} \right\rfloor + 1 \right\}$ ). Case 3: Reshape kernel weights that conduct convolution inside the input map. This case has  $S' \times S'$  reshaped weights, and each reshaped weight can be reused by t times ( $t \in \left\{ \left\lfloor \frac{LL-W+1}{S'} \right\rfloor^2, \left( \left\lfloor \frac{LL-W+1}{S'} \right\rfloor + 1 \right)^2, \left\lfloor \frac{LL-W+1}{S'} \right\rfloor \times \left( \left\lfloor \frac{LL-W+1}{S'} \right\rfloor + 1 \right)^2 \right)$ .

The pattern of W-CONV-S ZFDR is similar to that of T-CONV ZFDR. The difference is, for W-CONV of stride convolution, we remove zeros from  $\nabla$ output, reshape it as weight, then conduct convolution on input map to receive  $\nabla$ weight. W-CONV-S ZFDR has three cases as follows. **Case 1: Reshape zero-insertion**  $\nabla$ **output that conducts convolution at the corner of input map.** This case has  $\left\lceil \frac{P}{S} \right\rceil^2 + \left\lceil \frac{P-R}{S} \right\rceil^2 + 2 \left\lceil \frac{P}{S} \right\rceil \left\lceil \frac{P-R}{S} \right\rceil$  number of reshaped  $\nabla$ outputs and each of them is non-reusable. **Case 2: Reshape zero-insertion**  $\nabla$ **output that conducts convolution**

Fig. 13. 3D Connection Based on Original H-tree Connection.

on the edge of input map. This case has  $2\left\lceil \frac{P}{S} \right\rceil + 2\left\lceil \frac{P-R}{S} \right\rceil$  number of reshaped  $\nabla$ outputs, and each of them can be reused by I - (O-1)S times. Case 3: Reshape zero-insertion  $\nabla$ output that conduct convolution inside the input map. This case has only one zero-insertion  $\nabla$ output whose size is equal to  $\nabla$ output, and it can be reused by  $\left[I - (O-1)S\right]^2$  times.

Since both T-CONV ZFDR and W-CONV-S ZFDR have three similar types, we name them as *CornerReshape*, *EdgeReshape* and *InsideReshape* respectively. Note that *CornerReshape* has no reuse of reshaped weights while *InsideReshape* tends to have more reuses than *EdgeReshape* does. This involves an unbalance in runtime because *InsideReshape* takes a long time to execute while *CornerReshape* is idle in most of the time. Such unbalance not only exists in the executing stage, but also in the I/O transmission, because I/O connected to *InsideReshape* is busy while that connected to *CornerReshape* is slack. In order to address this problem, we duplicate *EdgeReshape* and *InsideReshape* for  $R_e$  times and  $R_i$  times respectively.

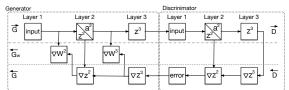

#### 4.2 3D-Connected PIM for GAN Training

In order to solve the problem elaborated in Sub-Section 3.2, we propose a 3D-connected PIM, aiming to efficiently fit dataflows of GAN training.

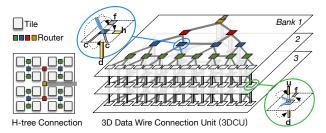

Fig.13 shows an original H-tree data wire connection in a bank with 16 tiles (light grey squares). Green and blue squares are multiplexing nodes, while red and yellow squares are merging nodes. To better illustrate our 3D connection architecture, we draw the connections as a binary tree and mark different connection layers with different colors. First, we add wires between two nodes whose parent nodes are different in one layer, such as the wire between the middle two blue nodes shown in Fig.13. Then we pile up three banks and add vertical wires between two corresponding nodes. For each two vertical connected nodes, the width of wire between them is the same as the width of wire connected to their parent nodes. Due to the pin bandwidth limitation, we modify the routers by adding switches. We take two nodes as examples shown in Fig.13 (original wires are colored grey and added wires are in yellow). For the node circled in blue, it has one switch, which can connect wire h, wire d or wire f, and two wires connected to child nodes are fixed as original. For the light gray node circled in green, it has two switches, which can connect *wire u*, *wire d* or *wire f*. Note that, only nodes in *Bank* 2 have two switches, which enable the nodes to connect both upper/down nodes at the same time. We create a state set *s\_set* for each switch, and we have

$s\_set \subseteq \{parent, horizontal, upper, down\}$ . Moreover, we add an adder into the each node, which can be also bypassed. Thus, we build a 3D data wire connection unit (3DCU), which can be configured into two modes: *Smode* for normal memory read/write and *Cmode* for computing. In *Smode*, the connections are static and configured as H-tree pattern. While in *Cmode*, the connections are dynamically reconfigured according to dataflows.

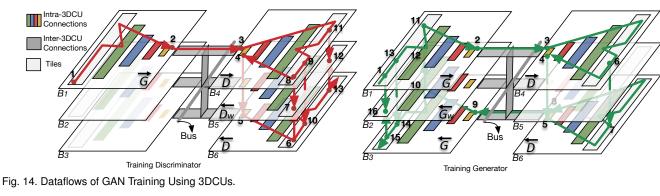

With 3DCU, we can build our 3D-connected PIM for training GANs. Fig.14 ellaborates how to use 3DCUs to train a GAN. First, we connect two 3DCUs ( $\{B_1, B_2, B_3\}$ ,  $\{B_4, B_5, B_6\}$ ) together. Banks in these two 3DCUs are all connected to the bus in traditional way. Moreover,  $B_1$  and  $B_4$ ,  $B_3$  and  $B_6$  can be connected to each other directly, bypassing the bus and CPU.

After connecting two 3DCUs, we first present the way of training discriminator in Fig.14. Note that we only present the critical concept paths, omitting other paths like data transferring of  $\nabla$ weight calculation inside the bank. When training discriminator,  $B_2$  and  $B_3$  are not used and stay in *Smode*, working as traditional memory. We first map G to  $B_1$  and D to  $B_4$ . After that, we configure  $\{B_1, B_4, B_5, B_6\}$ into Cmode. We show the dataflows of training discriminator with  $P_x$  (P reperesents the point marked on dataflows in Fig.14, x is the number of the point).  $P_1 \rightarrow P_2$  is the dataflow of  $\overline{G}$ , and the zigzag line represents that during G, we may transfer data from one tile to another tile through horizontal connections.  $P_2 \rightarrow P_3$  transfers outputs of generator to discriminator through the bypass bus connection.  $P_3 \rightarrow P_4$  shows the dataflow of D. During  $P_3 \rightarrow P_4$ , when we complete the computation of one layer, we map the corresponding part of  $D_w$  and D to  $B_5$  and  $B_6$  respectively. Note that we continue forward propagation of the discriminator when we map  $D_w$  and D. For example, we conduct  $P_{11} \rightarrow P_{12}$  and  $P_9 \rightarrow P_8$  simultaneously. We start the backward propagation by transferring error from  $P_4$  to  $P_5$ . During the backward propagation, we need the results from both  $\overrightarrow{D}$  ( $P_8 \rightarrow P_7, P_{11} \rightarrow P_{12}$ ) and  $\overleftarrow{D}$  ( $P_6 \rightarrow P_7, P_{13} \rightarrow P_{12}$ ) to conduct  $\overrightarrow{D_{w}}$ . Also, we need the result from  $\overrightarrow{D}$  ( $P_9

ightarrow P_{10}$ ) to conduct  $\overleftarrow{D}$ . After backward propagation, we configure  $\{B_4, B_5, B_6\}$  into *Smode*. Through reading  $B_5$ and some calculations in CPU, we update discriminator by writing new kernel weights to  $B_4$ .

The right part of Fig.14 illustrates the dataflows of training generator. Note that, after training discriminator,  $B_1$  is in *Cmode*, while others are in *Smode*. Thus, we first switch others to Cmode. At the same time, we can conduct G shown as  $P_1 \rightarrow P_2$ , and map  $G_w$ , G to  $B_2$ ,  $B_3$ simultaneously. Then we output results of  $\overrightarrow{G}$  to  $\overrightarrow{D}$  marked as  $P_2 \rightarrow P_3$  and start  $\overrightarrow{D}$  through  $P_3 \rightarrow P_4$ . Simultaneously, we map  $\overleftarrow{D}$  to  $B_6$ . After that, we start backward propagation by transferring error from  $P_4$  to  $P_5$ . The error is transferred to generator through  $P_5 \rightarrow P_8 \rightarrow P_9$ , and during this period, the result in  $\overrightarrow{D}$  is used for  $\overleftarrow{D}$ , such as  $P_6 \rightarrow P_7$ . After transferring error to  $\overleftarrow{G}$ , we start  $\overleftarrow{G}$  and  $\overleftarrow{G_w}$  in an interleaving way. Similar as dataflows in backward propagation of discriminator, we need  $P_{11} \rightarrow P_{12}$  and  $P_{10} \rightarrow P_{12}$ to conduct  $G_w$  first and then we need  $P_{13} \rightarrow P_{14}$  for G. Afterwards, we use  $P_1 \rightarrow P_{16}$  and  $P_{15} \rightarrow P_{16}$  to complete

Fig. 15. Data mappings on 3D-connected PIM.

$\overline{G_w}$ . Finally, in the same way of updating discriminator, we switch  $\{B_1, B_2, B_3\}$  to *Smode* and update generator.

In general, we map generator to one or several 3DCUs and map discriminator to corresponding 3DCUs connected to generator. The top layer is usually for forward propagation and the second, third layers are usually for  $\nabla$  weight calculation, error transfer respectively. We locate  $\nabla$ weight calculation in the second layer since it needs data transferred from either phases, while error transfer only needs data from forward propagation. What's more, in order to reduce data movement, we should make sure each part of phase is vertical alignment. Take computation between Layer1 and Layer2 in Fig.8 as an example. The left figure shown in Fig.15 is an original way of data mapping. The green and red parts are bigger than the blue one, because we apply ZFDR scheme on them, duplicating kernel weights for several times. For the blue one, it applies the normal kernel weight mapping pattern. This naive data mapping introduces non-negligible data movements, like blue lines marked in the left figure. We can solve this problem by splitting kernel weights and enable each part to handle corresponding vertical partial results (shown in the middle figure of Fig.15). Thus, we only need small-step data movements like  $C \rightarrow D$ . It's worth mentioning that green parts, red parts and blue parts are not vertical alignment perfectly. They may have small-step data movements horizontally, but it's much better than original data mapping shown in the left figure. The method in Step 1 is space-saving but less parallelism. Also, we can duplicate weights after splitting, like Step 2 shows. This improves the parallelism but turns out to be space consuming. The detailed design will be introduced in Section 5.

#### 4.3 Approximate Weight Update of GAN Training

In this sub-section, we propose an approximate weight update algorithm to mitigate the problem of high overhead caused by MLC programming (Section 3.3).

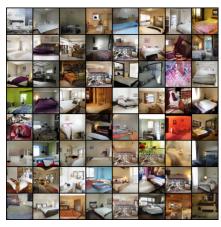

First, we are glad to observe that GANs can adapt to approximate computing. When we modify the lowsignificance bits of some weight values during GAN training, the quality of the samples generated by the trained

generator remains stable. For example, we first train DC-GAN in the standard procedure with the dataset bedroom in Lsun [69]. We use a 16-bit precision value to train the discriminator and generator iteratively. We train them 25 times with 50,000 iterations in each training round. Then we modify 20% weight values by changing their four lowsignificant bits randomly during the DCGAN training procedure. The pictures of bedrooms generated by these two trained generators are shown in Figure 17. The pictures generated from the modified training (Figure 17(b)) and pictures generated from the standard training (Figure 17(a)) look similar. To quantitatively compare these two trained GANs, we introduce FID in [46], a score to quantify the quality of the pictures generated. Experiments show that the difference between the FID of the original DCGAN and the FID of the modified-trained DCGAN is only 0.3. This means that the modified-trained DCGAN is virtually as good as the original one.

With training modified, we propose *Approximate Update*, an approximate weight update algorithm for GAN training. The key idea of *Approximate Update* is to avoid the energy-consuming SET operations in MLC writings without diminishing GANs' accuracy. Algorithm 1 shows the pseudo-code of the approximate weight update.

| Al  | gorithm 1: Approximate Weight Update                    |

|-----|---------------------------------------------------------|

| I   | <b>nput:</b> permission of approximate weight update to |

|     | the bitline: <i>permission</i> , set of values to be    |

|     | approximated: $[t_{down}, t_{up}]$ , current value:     |

|     | <i>c_value</i> , value to write: <i>w_value</i>         |

| 1 i | f $w_value == c_value$ then                             |

| 2   | Skip the write operation;                               |

| 3 e | lse                                                     |

| 4   | if $permission == FALSE$ or $w\_value \notin$           |

|     | $[t_{down}, t_{up}]$ then                               |

| 5   | Conduct normal MLC-write operation;                     |

| 6   | else                                                    |

| 7   | Conduct SET-sweep and RESET operations;                 |

|     | while $c\_value \notin [t_{down}, t_{up}]$ do           |

| 8   | Conduct SET and VERIFY operations;                      |

|     |                                                         |

The *Approximate Update* works with the *permission* indicating whether the bitline allows approximate computing. This is decided by the significance of the values. The  $[t_{down}, t_{up}]$  is set according to the pre-trained results to ensure the GAN's accuracy. In Algorithm 1, lines 1-2 show the

Fig. 16. Circuit of Approximate Update.

data-comparison-write module, which skips the write when the writing value equals the value of the cell. Then, lines 4-5 describe the conditions in which *Approximate Update* cannot be performed. Finally, lines 7-8 illustrate the procedure of *Approximate Update*, in which  $[t_{down}, t_{up}]$  includes values that require more fine-grained SET operations. The *Approximate Update* eliminates this time- and energy-intensive procedure by introducing crose-grained SET operations to enable  $c_value$  in  $[t_{down}, t_{up}]$  instead of forcing  $c_value = w_value$ .

Figure 16 depicts the circuit supporting *Approximate Update*, which is built on the data comparison write circuit. The red part of Figure 16 is the only part that differs from the data comparison write, because, in addition to determining whether two values are equal, it also judges whether the current value is in the given interval. Furthermore, the *Direct\_write* signal is controlled by line 4 in Algorithm 1.

# 5 LRGAN DESIGN

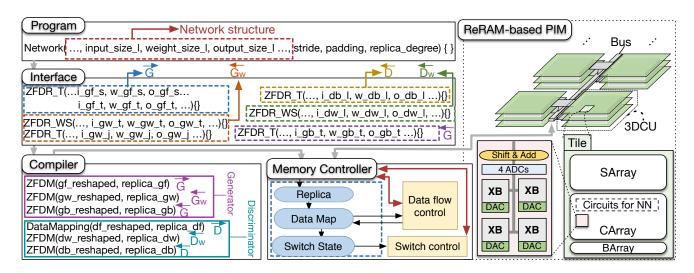

In this section, we present how the Zero-Free Scheme in Section 4.1 and 3D Connected PIM in Section 4.2 work together in LrGAN. Fig.18 elaborates the outline of LrGAN design in five parts.

**Program** In the program stage, we program a network, describing it layer by layer. For example, in the *l*th layer, we use the size of input (*input\_size\_l*), size of kernel weight (*weight\_size\_l*) and size of output (*output\_size\_l*) to describe it. Moreover, *stride* includes the stride of generator and stride of discriminator and so does *padding*. Structure *replica\_degree* describes the degree of duplication in each phase of training GAN. It has three degrees, *low*, *middle* and *high*. Programmers can easily use these three parameters which represent low to high parallelisms, without knowing how to duplicate kernel weights to increase parallelism, which will be performed by the compiler.

**Interface** We realize ZFDR by providing two interfaces. One is  $ZFDR_T$  for T-CONV ZFDR and the other is  $ZFDR_WS$  for W-CONV-S ZFDR. These two functions do not reshape data directly but create place holders and dataflows for further removing zeros, just like the way of traditional NN frameworks. Their parameters are passed from programming a network. These two functions also process the network layer by layer. The interface component in Fig.18 shows the most complex situation: the generator of this GAN has both T-CONV and S-CONV, and the discriminator has T-CONV. The generator needs  $ZFDR_T$  for  $\overrightarrow{G}$  (marked in blue), both  $ZFDR_T$  and  $ZFDR_WS$  for  $\overrightarrow{G}_w$  (marked in orange), and  $ZFDR_T$  for  $\overrightarrow{G}$  (marked in purple). The discriminator needs  $ZFDR_T$  for  $\overrightarrow{D}$  and  $\overrightarrow{D}_w$  (marked in yellow and green). Under normal situation where the generator has T-CONV and the discriminator has S-CONV,  $ZFDR_T$  is needed for  $\overrightarrow{G}$ ,  $\overrightarrow{G}_w$  and  $\overrightarrow{D}$ , and  $ZFDR_WS$  is for  $\overrightarrow{D}_w$ .

**Compiler** After reshaping data, we start to map them through a compiler. Mapping data has two parts. One is mapping generator and the other is mapping discriminator. In the case of the generator with both T-CONV and S-CONV, we map  $\overrightarrow{G}$ ,  $\overleftarrow{G_w}$ ,  $\overleftarrow{G}$ ,  $\overleftarrow{D_w}$  and  $\overleftarrow{D}$  by using Zero Free Data Mapping scheme (ZFDM), while we use normal data mapping scheme (DataMapping) to map  $\overrightarrow{D}$  (shown in the compiler component of Fig.18). In the case of the generator with only T-CONV, we use *DataMapping* for  $\overleftarrow{G}$  and  $\overrightarrow{D}$ , and ZFDM for the remaining phases. ZFDM has two main parameters: data reshaped by ZFDR and the number of replicas transferred from programming.

We take G to further elaborate ZFDM scheme. gf\_reshaped is data reshaped by ZFDR during generator forward propagation. *replica\_gf* is a vector which records the number of replicas in *CornerReshape*, *EdgeReshape* and InsideReshape. We name items in replica\_gf as *replica\_c, replica\_e* and *replica\_i*. Also, we calculate the average reuse time of each case and name them as *reuse\_c*, *reuse\_e* and *reuse\_i*. We do this because the reusing time of weights inside each case shows little difference. Assume that the time MMV consumed in CArray is  $t_m$ , then the total time of computation  $t_{c\_total}$  in a layer is  $t_m \times \frac{reuse\_i}{replica\_i}$  (the execution time of parallel tasks is decided by the longest task). We assume the time of transferring data from one tile to its neighbor is  $t_t$ , then transferring results of a layer to its next layer consumes at least  $\left(\left\lceil \frac{layer\_size}{CArray\_size} \right\rceil - 1\right) \times t_t$ , named  $t_{t \ total}$  (layer\_size is decided by replica\_c, replica\_e and  $replica_i$ ). We fix  $replica_c$  as 1 since  $reuse_c$  is 1, and define the maximum value  $replica_{emax}$ ,  $replica_{imax} =$  $LL \times replica\_e_{max}$  to let  $t_{t\_total} \leq t_{c\_total}$  (LL is the loop length defined in Section 4.1). Based on parameters defined above, we can define  $replica_q f$  as Table 4 shows.

TABLE 4 Value of *replica\_gf*.

| Value Part<br>Level | $replica_c$ | $replica_e$        | replica_i          |

|---------------------|-------------|--------------------|--------------------|

| low                 | 1           | 1                  | $replica\_e_{max}$ |

| middle              | 1           | $replica\_e_{max}$ | $replica\_e_{max}$ |

| high                | 1           | $replica\_e_{max}$ | $replica_{imax}$   |

To summarize, we duplicate kernel weights considering three factors: **(1) Programmers' demand (space demands)**. When the free space is small or programmers would like to use small memory space to train a GAN, they can set *replica\_degree* as *low*, and vise versa. **(2) Improving the performance.** More replicas indicate higher parallelism, which means higher performance. **(3) Avoiding I/O to become a bottleneck.** More replicas may incur more com-

(a) Pictures Generated under Normal Training.

(b) Pictures Generated under Modified Training.

Fig. 17. Comparison of Pictures Generated by The Normal Training and The Training with Modifying 4 Low Significant Bits of 20% Weight Values.

Fig. 18. Outline of LrGAN (an architecture combined techniques of ZFDR and 3DCUs).

munications among tiles, so we must avoid heavy communications from hindering performance. For other phases in ZFDM, parameters can be obtained in the same way of  $\vec{G}$  does.

Then we take  $\overrightarrow{D}$  to further introduce DataMapping scheme.  $df\_reshaped$  is data reshaped by normal reshaping scheme during forward propagation phase of discriminator. For  $replica\_df$ , we define it as Equation 14 shows, where  $s_{zf}$  is size of kernel weights after duplication in  $\overrightarrow{D}$  and  $s_n$  is size of kernel weights before duplication in  $\overrightarrow{D}$ .

$$replica\_df = \begin{cases} 1 & replica\_degree = low \\ \left\lfloor \frac{s_{zf}}{2 \times s_n} \right\rfloor & replica\_degree = middle \\ \left\lfloor \frac{s_{zf}}{s_n} \right\rfloor & replica\_degree = high \end{cases}$$

(14)

**Memory controller** Memory controller records the information transferred from the compiler, such as number of replicas and data mappings. What's more, it records states of switches, which are deduced by data mappings. These records come into a finite state machine, marked in blue rectangle in Memory Controller (Fig.18). The finite state machine offers states for dataflow controller and switch controller to control 3DCUs. Also, these two controllers receive signals from 3DCUs and update the finite state

machine. Thus, the memory controller can manage the data mapping and configure switches according to the dataflows dynamically.

**ReRAM-based PIM** The part communicating with memory controller is ReRAM-based PIM. It is also the main hardware that supports our LrGAN. It is configured with several 3DCU pairs introduced in Fig.14 in Section 4.2. Each tile in 3DCU contains *SArray*, *CArray* and *BArray*, using the design in PRIME [15], which has been already introduced in Section 2.1. The ReRAM crossbars in a *CArray* (marked in light pink in Fig.18) employ the design of that in ISAAC [58], since they can support 16-bit precision data while PRIME can not. Based on the tile equipped with basic NN computation and storage ability, our proposed 3DCU pairs can work well.

# 6 EVALUATION

In this section, we first introduce our experimental setup and benchmarks used to evaluate the proposed designs. We then present our evaluation results in terms of performance, energy, and overhead.

#### 6.1 Experimental Setup

We compare LrGAN with (1) GANs running on GPU platform; (2) FPGA-based GAN accelerator [50]; and (3) GANs running on modified ReRAM-based NN accelerator: PRIME [15]. We use the NVIDIA Titan X as our GPU platform and choose the Xilinx VCU118 board for implementing FPGA-based GAN accelerator. The hardware configurations we used for PRIME and LrGAN are listed in Table 5. The configurations of ReRAM are from [16], [53], [68].

|                |          | Intel Xeon CPU E5520,               |  |  |  |

|----------------|----------|-------------------------------------|--|--|--|

| Host Processor |          | 2.27GHz, 4 cores                    |  |  |  |

|                | -        | ,                                   |  |  |  |

| L1 I/D cache   |          | 32KB/32KB; 4-way; 2 cycles access   |  |  |  |

| L2 cacl        | ne       | 256KB; 8-way; 10 cycles access      |  |  |  |

|                | Overview | $TaO_x/TiO_2$ -based ReRAM          |  |  |  |

| ReRAM-based    |          | 16GB; 2GB per bank, 128MB per tile; |  |  |  |

| Main Memory    |          | SET/RESET/ latency: 100/34 ns;      |  |  |  |

|                | Bank     | read latency: 16 ns                 |  |  |  |

|                |          | SET/RESET energy: 9/10 pJ           |  |  |  |

|                |          | read energy: 2 pJ                   |  |  |  |

|                | H-Tree   | 29.9ns latency, 386pJ energy        |  |  |  |

| I/O Frequency  |          | 1.6GHz                              |  |  |  |

TABLE 5 Hardware Configurations.

For LrGAN configuration, we use 4-bit for each ReRAM cell, and 16-bit for input, weight and output (i.e. same as [61]). The size of ReRAM array is  $128 \times 128$  cells. We configure half of a tile for CArray (64MB), 1/64 of the tile for BArray (2MB) and the remaining 62MB for SArray. We use CACTI-6.5 [51], CACTO-IO [29] to model our interconnects and off-chip connects respectively.

## 6.2 Benchmarks

We employ 8 state-of-the-art GAN networks as our benchmarks, shown in Table 6. To describe the topologies of GANs, we use f, c and t to denote fully-connected, convolution and transposed convolution layers respectively. For example, the 512c5k2s denotes a convolution layer with 512 input feature maps, using  $5 \times 5 \times 512$  kernels with a stride of 2, while 2s in 512t5k2s denotes a transposed convolution layer with a stride of 1/2. The 100*f* denotes a fully-connected layer with 100-unit input and f1 denotes a fully-connected layer with 1-unit output. The t3 represents that after T-CONV, there are 3 output feature maps. For simplicity, if several layers share the same size of kernel or stride, we consolidate those common factors at the end, for example 100f-(1024t-512t-256t-128t)(5k2s)-t3, where layers 1024t, 512t, 256t, and 128t share the common kernel size of 5 and stride size of 2.

# 6.3 Results

We fully train the networks in Table 6 with the batch size of 64, and the results are shown as follows.

We first examine the effectiveness of our proposed *ZFDR* and 3D connection mechanisms. We then compare the performance and energy between LrGAN and alternative PIM design such as PRIME. Moreover, we compare Lr-GAN with FPGA-based GAN accelerator and GAN running on GPU platform. Note that we use 2D and 3D to represent H-tree and 3D connection design, respectively, and investigate configurations with different degrees of duplication (i.e. low, middle and high).

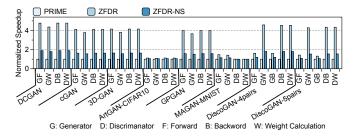

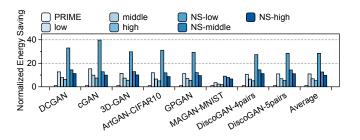

Fig. 19. Performance Comparison on Phases used ZFDR with PRIME

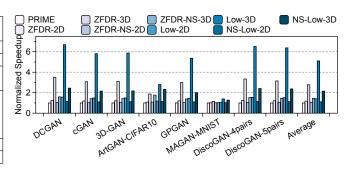

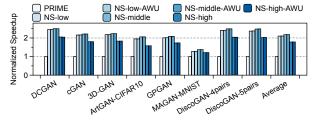

Fig. 20. Performance Comparison between 3D-Connection and H-tree Connection with ZFDR

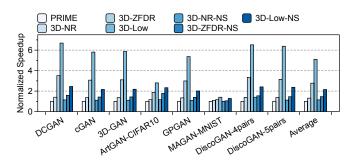

Fig. 21. Performance Comparison between ZFDR and Normal Reshape with 3D-Connection

Fig.19 shows the performance of ZFDR in different GAN phases. We use NS to represent normalized space, which means that PRIME uses the same CArray space as our design. ZFDR achieves distinct speedup on DCGAN, cGAN, 3D-GAN, GPGAN and DiscoGAN, which reflects that there are large portions of zeros in these GANs. What's more, ZFDR saves up to  $5.2 \times$  SArray space for storing inputs (in the case of DCGAN), and saves  $3.86 \times$  SArray space on average. Note that DiscoGAN-4pairs has 5 phases using ZFDR because its generator has both S-CONV and T-CONV. Moreover, there is no speedup on discriminator of MAGAN-MNIST, because its layers are fully-connected.

When we evaluate the entire process of training GANs with H-tree connection, the speedup of ZFDR almost disappears. This is resulted from the overhead of data transfers. Fig.20 shows the performance of our 3D connection design compared with H-tree connection. We observe that with our 3D connection design, the speedup of ZFDR is much more visible. Moreover, with 3D connection, duplication (low degree) achieves much higher performance speedup than ZFDR with no duplication, while duplication achieves

TABLE 6

Topologies of GAN benchmarks. (f:fully-connected c: convolution t:transposed convolution k:kernel s:stride)

| Name                 | Generator                                                            | Item Size      | Discriminator                      |  |

|----------------------|----------------------------------------------------------------------|----------------|------------------------------------|--|

| DCGAN [71]           | DCGAN [71] 100f-(1024t-512t-256t-128t)(5k2s)-t3                      |                | (3c-128c-256c-512c-1024c)(5k2s)-f1 |  |

| cGAN [55]            | 100f-(256t-128t-64t)(4k2s)-t3                                        | $64 \times 64$ | (3c-64c-128c-256c)(4k2s)-f1        |  |

| 3D-GAN [66]          | N [66] 100f-(512t-256t-128t)(4k2s)-t3 64                             |                | (1c-64c-128c-256c-512c)(4k2s)-f1   |  |

| ArtGAN-CIFAR-10 [63] | 100f-1024t4k1s-512t4k2s-256t4k2s-128t4k2s-                           | $32 \times 32$ | 3c4k2s-128c3k1s-(128c-256c-512c-   |  |

|                      | 128t3k1s-t3                                                          | 32 X 32        | 1024c)(4k2s)-f11                   |  |

| GPGAN [65]           | GPGAN [65] 100f-(512t-256t-128t-64t)(4k2s)-t3                        |                | (3c-64c-128c-256c-512c)(4k2s)-f1   |  |

| MAGAN-MNIST [64]     | 50f-128t7k1s-64t4k2s-t1                                              | $28 \times 28$ | 784f-256f-256f-784f-f11            |  |

| DiscoGAN-4pairs [31] | (3c-64c-128c-256c-512t-256t-128t-64t)(4k2s)-t3                       | $64 \times 64$ | (3c-64c-128c-256c-512c)(4k2s)-f1   |  |

| DiscoGAN-5pairs [31] | (3c-64c-128c-256c-512c)(4k2s)-100f-(512t-256t-<br>128t-64t)(4k2s)-t3 | $64 \times 64$ | (3c-64c-128c-256c-512c)(4k2s)-f1   |  |

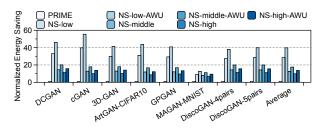

Fig. 22. Performance Comparison between LerGAN and PRIME (without Approximate Weight Update)

Fig. 23. Energy Saving Comparison between LerGAN and PRIME (without Approximate Weight Update)

little speedup with H-tree connection.

Fig.21 compares the performance between ZFDR and normal reshaping (marked as NR) with 3D connection. The results show that with 3D connection, ZFDR with (without) duplication achieves  $5.11 \times (2.77 \times)$  speedup on average, while normal reshaping only yields  $1.31 \times$  speedup, indicating that both our 3D connection design and ZFDRare critical to accelerate GAN execution.

Experiments above show that *ZFDR* and 3D connection can achieve high speedup when they work together. We further show the performance of LerGAN which combines these two techniques. It's worth to mention that we use Ler-GAN and LrGAN to represent the PIM architecture without and with the approximate update scheme, respectively. We train the discriminator and generator of each GAN for ten iterations and calculate the average time of each iteration. We compare different duplication degrees of LerGAN with PRIME, shown in Fig.22. First of all, with our design applied without approximate updating, DCGAN has more speedup than 3D-GAN and GPGAN because it has a larger kernel size than others, which leads to a larger proportion of multiplications with zeros. Besides, MAGAN-MNIST shows nearly no speedup since its discriminator is fully-connected

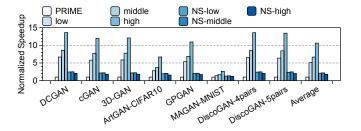

Fig. 24. Performance Comparison between LerGAN and LrGAN

Fig. 25. Energy Saving Comparison between LerGAN and LrGAN

and its generator is small with only one T-CONV.

Fig.23 shows the results of energy saving. Note that LerGAN-low-NS achieves 28.47× energy saving on average. This energy saving owes much to our zero-free and 3D connection design, since they reduce the amount of data as well as the data movements requiring long wires. Besides, with the increase of duplications, LerGAN exhibits less energy saving, since more duplications leads to (1) more memory writes when updating GANs; and (2) more complex and energy-consuming switch configurations.

We then evaluate the performance and energy saving of *Approximate Update*. We set permissions of (4x + 3)th and (4x + 4)th columns as TRUE, and others are FALSE  $(0 \le x \le 31)$ . For (4x + 3)th columns,  $[t_{down}, t_{up}]$  is [6, 9], and  $[t_{down}, t_{up}]$  is [4, 11] in (4x + 4)th columns. It is worth to mention that these configurations obtained through various experiments are not optimal. We leave how to find the optimal solution as our future work.

Fig.24 and Fig.25 depict the speedup and energy saving results of LrGAN with *Approximate Update* compared with PRIME and lerGAN without *Approximate Update*. In both of them, AWU represents approximate weight update algorithm. From Fig.24 we can figure out that *Approximate Update* are unable to achieve speedup because the latency of each write operation is decided by the longest latency of programming cells in a row. Since the (4x + 1)th and (4x + 2)th columns employ normal programming model,

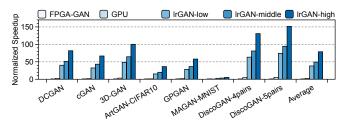

Fig. 26. Performance Comparison among FPGA-based GAN accelerator, GPU platform and LrGAN

Fig. 27. Energy Saving Comparison among FPGA-based GAN accelerator, GPU platform, LerGAN and LrGAN

they keep the longest latency unchanged. However, *Approximate Update* can achieve  $1.4 \times$  energy saving on average as shown in Fig.25, which finally achieves  $40 \times$  energy saving on low-duplication mode when compared with PRIME. This mainly benefits from avoiding high energy-consuming fine-grain programming scheme.

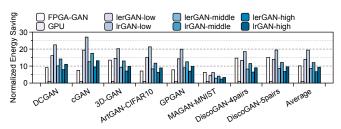

We also compare LrGAN with the FPGA-based GAN accelerator and GPU platform. Fig.26 and 27 show the performance and energy consumption of aforementioned architectures, respectively. In terms of the performance, since our approximate update scheme has no speedup on LerGAN, we show the results of LrGAN (the speedup of LerGAN is the same with that of LrGAN). LrGAN achieves  $47.2 \times$  and  $21.42 \times$  speedup on average over FPGA-GAN and GPU, respectively. What's more, DiscoGAN manifests more speedup over others because (1) it has more T-CONVs, which means more zeros. Our LrGAN with ZFDR design shows higher performance; (2) the size of DiscoGAN is bigger, leading to more off-chip memory accesses for FPGA and GPU, which causes PIM-based LrGAN to perform better. Moreover, GANs with small sizes, such as MAGAN-MNIST, and lacking T-CONVs, cause less speedup. For the energy saving, LerGAN-low and LrGAN-low save more energy than FPGA-based GAN accelerator for GANs with small size but with more frequent T-CONVs (the left five GANs in Fig.26). However, for GANs with small size and fewer T-CONVs (MAGAN-MNIST), LerGAN shows slightly less energy saving than what FPGA-GAN accelerator performs. This is because LerGAN consumes more energy when updating networks. Consequently, the extra energy cost can not be amortized by the energy-saving opportunity. Thanks to our approximate weight update algorithm, LrGAN has  $1.34 \times$  energy saving than the FPGA-GAN accelerator on average. Moreover, as shown in Fig.26 and 27, though more duplication (e.g., LrGAN-high) brings more speedup, it results in more energy consumption.

Fig. 28. The Breakdown of Energy Fig. 29. The Consumption in LrGAN (Overall) Consumption

### Fig. 29. The Breakdown of Energy Consumption of a ReRAM Tile

# 6.4 Accuracy Loss

We employ *FID* (Fréchet Inception Distance) in [46] to quantify the quality of the pictures generated. *FID* is a score that reflects **the distance between a real and a fake item in the feature level** (the next-to-last layer). Therefore, a lower FID means both higher quality and higher diversity of the generated item. We can calculate *FID* by Equation 15.

$$FID = ||\mu_r - \mu_g||^2 + T_r(\sum_r + \sum_g - 2(\sum_r \sum_g)^{\frac{1}{2}}) \quad (15)$$

In Equation 15, r and g represent real items and generated items;  $\mu$  is the mean of the feature;  $T_r$  is the sum of all the diagonal elements;  $\sum$  is the covariance matrix of features. In experiments, it's difficult for a human to decipher a generated item from a real one when the difference between the two *FIDs* is less than 5.

We set the same noise to train each GAN when comparing the standard training and the approximate training. The accuracy loss calculated by  $FID_{app} - FID_o$  is shown in Table 7, which shows the accuracy of our proposed algorithm is guaranteed.

TABLE 7 Accuracy Loss of Approximate Weight Update.

| Name            | FIDo | $FID_{app}$ | Difference |

|-----------------|------|-------------|------------|

| DCGAN           | 35.6 | 36.5        | 0.9        |

| cGAN            | 64.0 | 64.7        | 0.7        |

| 3D-GAN          | 30.3 | 31.6        | 1.3        |

| ArtGAN-CIFAR-10 | 32.5 | 33.0        | 0.5        |

| GPGAN           | 40.7 | 41.5        | 0.8        |

| MAGAN-MNIST     | 3.2  | 4.7         | 1.5        |

| DiscoGAN-4pairs | 29.4 | 29.9        | 0.5        |

| DiscoGAN-5pairs | 29.4 | 29.9        | 0.5        |

# 6.5 Energy Distribution

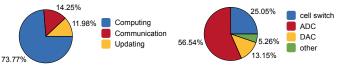

Fig.28 shows the overall energy distribution of LrGAN executed across the experimented benchmarks. The energy of computing dominates 73.77% of the total energy in Lr-GAN since it has a large amount of ReRAM-tile-related operations, while that of communication occupies 14.25%, benefited from our 3D-connected PIM design. Moreover, we break down the energy distribution of a ReRAM tile, as shown in Fig.29. The results show that cell switching (25.05%) and ADC (56.54%) are the two main energy-consuming contributors. Several studies [70] [38] on materials contribute on reducing energy consumption of cell switching and ADC. If LrGAN is equipped with 1-pJ cell switching [70], and a more energy-saving ADC (e.g. 60% [38]), it can achieve nearly  $3 \times$  power reduction.

## 6.6 Overhead

The overhead of LrGAN has two parts: software overhead and hardware overhead. For the software overhead caused

by *ZFDR* and *ZFDM*, LrGAN spends 32.52% more time than traditional methods on compiling. However, compared with the total time spent on training a GAN(e.g. several days), the overhead of few minutes incurred by the software overhead can be ignored. For the hardware, we add some switches, wires and modified circuit of *Approximate Update*. All of these cause 13.5% space overhead compared with PRIME. However, this space overhead can be justified by the higher performance ( $2.1 \times$  speedup) delivered by LrGAN, compared with PRIME using the same space. What's more, *Approximate Update* has only 0.9% time and 0.2% energy overheads.

# 7 RELATED WORK

**3D** Network on Chip (NoC) There are several prior studiess on 3D NoC [39] [30] [54] [8] [1], which are proposed for shortening connections. However, their complex routing algorithms are not suitable for GAN, while our succinct 3D connection design fits GAN well.

NN accelerators Many recent works accelerate NN based on FPGAs [72] [47] [74] [59] [3] and ASICs [19] [24] [73] [41] [12] [44] [57] [45] [2]. Diannao family was proposed based on Near-Data Processing (NDP) [11] [13] [17] [42], which locates processors near the memory to reduce the overhead of off-chip memory access. Our design is based on ReRAM-based PIM, further reducing data movements.

**ReRAM-based NN accelerators** PRIME [15] is an accelerator on basic computations of inference like MMV computation. ISAAC [58] proposed a pipeline solution to accelerate inference of CNNs. PipeLayer [61] further proposed a pipeline solution with intra-layer parallelism on both inference and training of CNNs. TIME [14] proposed a ReRAM-based training-in-memory architecture and further reduced the frequency of ReRAM read/write. Our work proposes a zero-free, 3D connected GAN accelerator.

GAN accelerators Song et.al. [50] proposed FPGA-based GAN accelerator. It uses well-designed dataflows to remove zero operations and increase data reuse on FPGA. Amir et.al. proposed a SIMD-MIMD acceleration for GAN [5] [4] [6], by removing zeros in GAN training. Chen et.al. proposed ReGAN, a ReRAM-based GAN accelerator using pipeline [10] design. Our LrGAN design is PIM-based and flexible to handle all zero-related scenarios in GAN training.

## 8 CONCLUSIONS

In this paper, we propose a high-performance, energyefficient PIM-based GAN accelerator: LrGAN. We design an NVM-based PIM which outperforms the FPGA-based GAN accelerator and GPU in both performance and energy consumption when training GANs. This offsets the flexibility of PIM, which is worse than FPGA and GPU. LrGAN has three main techniques: (1) the Zero-Free Data Reshaping (*ZFDR*) scheme designed for ReRAM-based PIM to remove computations with zeros; (2) the reconfigurable 3D connection in PIM which eliminates the bottleneck of long data movement; and (3) the approximate weight update scheme which prevents unnecessary energy-inefficient fine-grained MLC programming. LrGAN also combines these techniques with minor modifications of software and memory controller. Experiments show that LrGAN achieves  $47.2 \times$ ,  $21.42 \times$ , and  $7.46 \times$  speedup over the FPGA-based GAN accelerator, GPU platform, and PRIME respectively. Moreover, LrGAN delivers  $13.65 \times$ ,  $10.75 \times$ , and  $1.34 \times$  energy savings over the GPU platform, PRIME, and the FPGA-based GAN accelerator, respectively.

# ACKNOWLEDGMENTS

This work is supported by National Key Research & Development Program of China (Grant No.2018YFB1003301), the National Natural Science Foundation of China (Grant No.61832011), Research and Development Plan in Key Field of Guangdong Province (Grant No.2018B010109002).

# REFERENCES

- A. B. Ahmed and A. B. Abdallah, "La-xyz: low latency, high throughput look-ahead routing algorithm for 3d network-on-chip (3d-noc) architecture," in *Embedded Multicore Socs* (MCSoC), 2012 IEEE 6th International Symposium on. IEEE, 2012, pp. 167–174.

- [2] J. Albericio, P. Judd, T. Hetherington, T. Aamodi, N. E. Jerger, and A. Moshovos, "Cnvlutin: Ineffectual-neuron-free deep neural network computing," in ACM SIGARCH Computer Architecture News, vol. 44, no. 3. IEEE Press, 2016, pp. 1–13.

- [3] M. Alwani, H. Chen, M. Ferdman, and P. Milder, "Fused-layer cnn accelerators," in *Microarchitecture (MICRO)*, 2016 49th Annual IEEE/ACM International Symposium on. IEEE, 2016, pp. 1–12.

- [4] Y. Amir, F. Hajar, J. W. Philip, S. Kambiz, E. Hadi, and S. K. Nam, "Ganax: A unified simd-mimd acceleration for generative adversarial network," in *IEEE/ACM International Symposium on Computer Architecture (ISCA)*, 2018.

- [5] Y. Amir, S. Kambiz, E. Hadi, and S. K. Nam, "A simd-mimd acceleration with access-execute decoupling for generative adversarial networks," in *SysML Conference (SysML)*, 2018.

- [6] Y. Amir, B. Michael, K. Behnam, G. Soroush, S. Kambiz, E. Hadi, and S. K. Nam, "Fxgan: A unified mimd-simd fpga acceleration with decoupled access-execute units for generative adversarial networks," in *IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, 2018.

- [7] M. N. Bojnordi and E. Ipek, "Memristive boltzmann machine: A hardware accelerator for combinatorial optimization and deep learning," in *High Performance Computer Architecture (HPCA)*, 2016 *IEEE International Symposium on*. IEEE, 2016, pp. 1–13.

- [8] C.-H. Chao, K.-Y. Jheng, H.-Y. Wang, J.-C. Wu, and A.-Y. Wu, "Traffic-and thermal-aware run-time thermal management scheme for 3d noc systems," in *Networks-on-Chip* (NOCS), 2010 Fourth ACM/IEEE International Symposium on. IEEE, 2010, pp. 223–230.

- [9] O. Chapelle, B. Scholkopf, and A. Zien, "Semi-supervised learning (chapelle, o. et al., eds.; 2006)[book reviews]," *IEEE Transactions on Neural Networks*, vol. 20, no. 3, pp. 542–542, 2009.

- [10] F. Chen, L. Song, and Y. Chen, "Regan: a pipelined reram-based accelerator for generative adversarial networks," in *Proceedings of* the 23rd Asia and South Pacific Design Automation Conference. IEEE Press, 2018, pp. 178–183.

- [11] T. Chen, Z. Du, N. Sun, J. Wang, C. Wu, Y. Chen, and O. Temam, "Diannao: A small-footprint high-throughput accelerator for ubiquitous machine-learning," ACM Sigplan Notices, vol. 49, no. 4, pp. 269–284, 2014.

- [12] Y.-H. Chen, T. Krishna, J. S. Emer, and V. Sze, "Eyeriss: An energyefficient reconfigurable accelerator for deep convolutional neural networks," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 1, pp. 127–138, 2017.

- [13] Y. Chen, T. Luo, S. Liu, S. Zhang, L. He, J. Wang, L. Li, T. Chen, Z. Xu, N. Sun et al., "Dadiannao: A machine-learning supercomputer," in Proceedings of the 47th Annual IEEE/ACM International Symposium on Microarchitecture. IEEE Computer Society, 2014, pp. 609–622.

- [14] M. Cheng, L. Xia, Z. Zhu, Y. Cai, Y. Xie, Y. Wang, and H. Yang, "Time: A training-in-memory architecture for memristor-based deep neural networks," in *Proceedings of the 54th Annual Design Automation Conference* 2017. ACM, 2017, p. 26.

- [15] P. Chi, S. Li, C. Xu, T. Zhang, J. Zhao, Y. Liu, Y. Wang, and Y. Xie, "Prime: a novel processing-in-memory architecture for neural network computation in reram-based main memory," in ACM SIGARCH Computer Architecture News, vol. 44, no. 3. IEEE Press, 2016, pp. 27–39.

- [16] X. Dong, "Modeling and leveraging emerging non-volatile memories for future computer designs," 2011.

- [17] Z. Du, R. Fasthuber, T. Chen, P. Ienne, L. Li, T. Luo, X. Feng, Y. Chen, and O. Temam, "Shidiannao: Shifting vision processing closer to the sensor," in ACM SIGARCH Computer Architecture News, vol. 43, no. 3. ACM, 2015, pp. 92–104.

- [18] D. Erhan, Y. Bengio, A. Courville, P.-A. Manzagol, P. Vincent, and S. Bengio, "Why does unsupervised pre-training help deep learning?" *Journal of Machine Learning Research*, vol. 11, no. Feb, pp. 625–660, 2010.

- [19] C. Farabet, B. Martini, B. Corda, P. Akselrod, E. Culurciello, and Y. LeCun, "Neuflow: A runtime reconfigurable dataflow processor for vision," in *Computer Vision and Pattern Recognition Workshops* (CVPRW), 2011 IEEE Computer Society Conference on. IEEE, 2011, pp. 109–116.

- [20] A. Farmahini-Farahani, J. H. Ahn, K. Morrow, and N. S. Kim, "Nda: Near-dram acceleration architecture leveraging commodity dram devices and standard memory modules," in *High Performance Computer Architecture (HPCA)*, 2015 IEEE 21st International Symposium on. IEEE, 2015, pp. 283–295.

- [21] C. Finn, I. Goodfellow, and S. Levine, "Unsupervised learning for physical interaction through video prediction," in Advances in neural information processing systems, 2016, pp. 64–72.

- [22] A. Ghosh, B. Bhattacharya, and S. B. R. Chowdhury, "Sad-gan: Synthetic autonomous driving using generative adversarial networks," arXiv preprint arXiv:1611.08788, 2016.

- [23] A. Graves, A.-r. Mohamed, and G. Hinton, "Speech recognition with deep recurrent neural networks," in *Acoustics, speech and signal processing (icassp)*, 2013 ieee international conference on. IEEE, 2013, pp. 6645–6649.

- [24] S. Han, X. Liu, H. Mao, J. Pu, A. Pedram, M. A. Horowitz, and W. J. Dally, "Eie: efficient inference engine on compressed deep neural network," in *Computer Architecture (ISCA)*, 2016 ACM/IEEE 43rd Annual International Symposium on. IEEE, 2016, pp. 243–254.

- [25] T. Hastie, R. Tibshirani, and J. Friedman, "Unsupervised learning," in *The elements of statistical learning*. Springer, 2009, pp. 485–585.

- [26] G. Hinton, L. Deng, D. Yu, G. E. Dahl, A.-r. Mohamed, N. Jaitly, A. Senior, V. Vanhoucke, P. Nguyen, T. N. Sainath *et al.*, "Deep neural networks for acoustic modeling in speech recognition: The shared views of four research groups," *IEEE Signal processing magazine*, vol. 29, no. 6, pp. 82–97, 2012.

- [27] C.-W. Hsu, I.-T. Wang, C.-L. Lo, M.-C. Chiang, W.-Y. Jang, C.-H. Lin, and T.-H. Hou, "Self-rectifying bipolar tao x/tio 2 rram with superior endurance over 10 12 cycles for 3d high-density storageclass memory," in VLSI Technology (VLSIT), 2013 Symposium on. IEEE, 2013, pp. T166–T167.

- [28] G. Huang, S. Song, J. N. Gupta, and C. Wu, "Semi-supervised and unsupervised extreme learning machines," *IEEE transactions* on cybernetics, vol. 44, no. 12, pp. 2405–2417, 2014.

- [29] N. P. Jouppi, A. B. Kahng, N. Muralimanohar, and V. Srinivas, "Cacti-io: Cacti with off-chip power-area-timing models," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 7, pp. 1254–1267, 2015.

- [30] J. Kim, C. Nicopoulos, D. Park, R. Das, Y. Xie, V. Narayanan, M. S. Yousif, and C. R. Das, "A novel dimensionally-decomposed router for on-chip communication in 3d architectures," ACM SIGARCH Computer Architecture News, vol. 35, no. 2, pp. 138–149, 2007.

- [31] T. Kim, M. Cha, H. Kim, J. Lee, and J. Kim, "Learning to discover cross-domain relations with generative adversarial networks," arXiv preprint arXiv:1703.05192, 2017.

- [32] A. Krizhevsky, I. Sutskever, and G. E. Hinton, "Imagenet classification with deep convolutional neural networks," in *Advances in neural information processing systems*, 2012, pp. 1097–1105.

- [33] H. Kwon, A. Samajdar, and T. Krishna, "Maeri: Enabling flexible dataflow mapping over dnn accelerators via reconfigurable interconnects," ACM SIGPLAN Notices, vol. 53, no. 2, pp. 461–475, 2018.

- [34] Y. LeCun, Y. Bengio, and G. Hinton, "Deep learning," *nature*, vol. 521, no. 7553, p. 436, 2015.

- [35] C. Ledig, L. Theis, F. Huszár, J. Caballero, A. Cunningham, A. Acosta, A. Aitken, A. Tejani, J. Totz, Z. Wang *et al.*, "Photorealistic single image super-resolution using a generative adver-

sarial network," in Proceedings of the IEEE conference on computer vision and pattern recognition, 2017, pp. 4681–4690.

- [36] H. Lee, Y. Chen, P. Chen, P. Gu, Y. Hsu, S. Wang, W. Liu, C. Tsai, S. Sheu, P. Chiang *et al.*, "Evidence and solution of over-reset problem for hfo x based resistive memory with sub-ns switching speed and high endurance," in *Electron Devices Meeting (IEDM)*, 2010 IEEE International. IEEE, 2010, pp. 19–7.

- [37] M.-J. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, Y.-B. Kim, C.-J. Kim, D. H. Seo, S. Seo *et al.*, "A fast, high-endurance and scalable non-volatile memory device made from asymmetric ta 2 o 5- x/tao 2- x bilayer structures," *Nature materials*, vol. 10, no. 8, p. 625, 2011.